Petter Reinholdtsen: Free software toolchain for the simplest RISC-V CPU in a small FPGA?

On Wednesday I had the pleasure of attending a presentation organized

by the Norwegian Unix Users Group on

implementing

RISC-V using a small FPGA. This project is the result of a

university teacher wanting to teach students assembly programming

using a real instruction set, while still providing a simple and

transparent CPU environment. The CPU in question implements the

smallest set of opcodes needed to still call the CPU a RISC-V CPU,

the

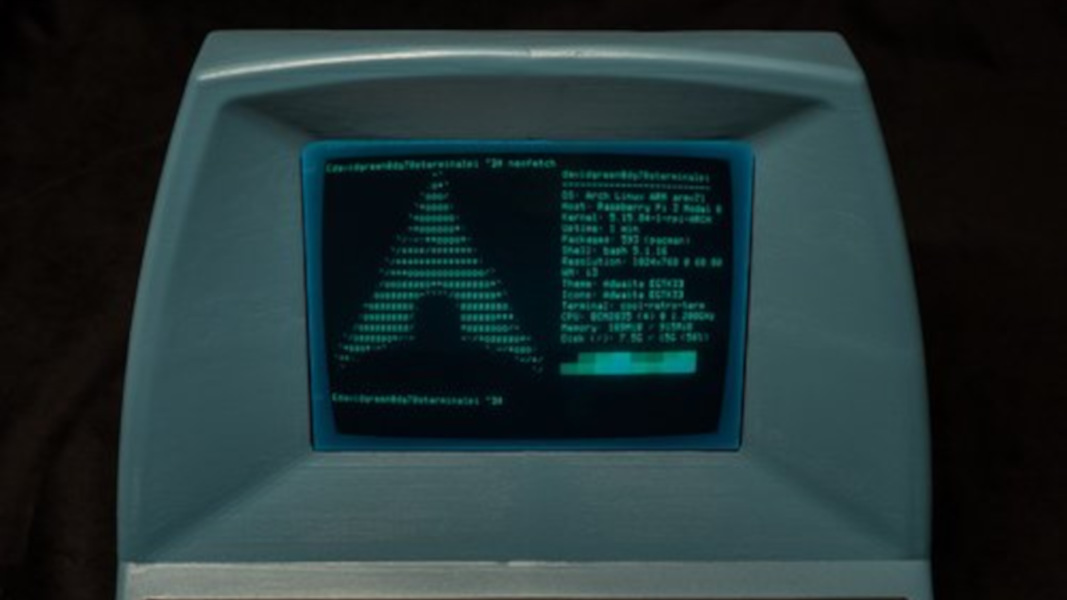

RV32I base set. The author and presenter, Kristoffer Robin

Stokke, demonstrated how to build both the FPGA setup and a small

startup code providing a “Hello World” message over both serial port

and a small LCD display. The FPGA is programmed using VHDL,

the entire source

code is available from github, but unfortunately the target FPGA

setup is compiled using the proprietary tool Quartus. It is such

a pity that such a cool little piece of free software should be

chained down by non-free software, so my friend Jon Nordby set out to

see if we can liberate this small RISC-V CPU. After all, it would be

unforgivable sin to force students to use non-free software to study

at the University of Oslo.

The VHDL code for the CPU instructions itself is only 1138 lines,

if I am to believe wc -l lib/riscv_common/* lib/rv32i/*. On

the small FPGA used during the talk, the entire CPU, ROM, display and

serial port driver only used up half the capacity. These days, there

exists a free software toolchain for FPGA programming not only in

Verilog but also in VHDL, and we hope the support in

yosys,

ghdl, and

yosys-plugin-ghdl

(sadly and strangely enough, removed from Debian unstable) is complete

enough to at least build this small and simple project with some minor

portability fixes. Or perhaps there are other approaches that work

better? The first patches are already floating on github, to make the

VHDL code more portable and to test out the build. If you are

interested in running your own little RISC-V CPU on a FPGA chip,

please get in touch.

At the moment we sadly have hit a GHDL bug, which we do not quite

know how to work around or fix:

******************** GHDL Bug occurred *************************** Please report this bug on https://github.com/ghdl/ghdl/issues GHDL release: 5.0.1 (Debian 5.0.1+dfsg-1+b1) [Dunoon edition] Compiled with unknown compiler version Target: x86_64-linux-gnu /scratch/pere/src/fpga/memstick-fpga-riscv-upstream/ Command line: Exception CONSTRAINT_ERROR raised Exception information: raised CONSTRAINT_ERROR : synth-vhdl_expr.adb:1763 discriminant check failed ******************************************************************

Thus more work is needed. For me, this simple project is the first

stepping stone for a larger dream I have of converting the MESA

machine controller system to build its firmware using a free

software toolchain. I just need to learn more FPGA programming

first. 🙂

As usual, if you use Bitcoin and want to show your support of my

activities, please send Bitcoin donations to my address

15oWEoG9dUPovwmUL9KWAnYRtNJEkP1u1b.